I'm

Sarthak Gupta

I'm

Brief About Me

Hardware Descriptive Languages: Verilog, System Verilog, VHDL

90%

Simulation Languages: Python, MATLAB

85%

Embedded Design Languages: C, C++, Embedded C, Wiring

90%

Misc. Languages: Latex, HTML, CSS

75%

Hardware Design/Simulation Tools: Xilinx Vivado, Eclipse (with ARM plugin), Eagle, Altium

85%

IC Design/Simulation Tools: Synopsys Verdi, Cadence SimVision, Cadence Virtuoso

85%

My Resume

Research

Invited speaker in workshop titled "Deep Learning: Perspectives, Trends AND Research Prospects" organized by Department of Computer Applications, Rosary College of Commerce and Arts, Goa.

Invited speaker in workshop titled "Hands on Introduction to Deep Learning using Tensorflow" organized by IEEE-IISc branch in Indian Institute of Science (IISc), Bangalore.

Invited speaker in workshop titled "Introduction to Machine Learning using Tensorflow" organized by IEEE-IISc branch in Indian Institute of Science (IISc), Bangalore.

Research/Academic Work

It was a master thesis project. Proposed and implemented the hardware design of reservoir network which can perform real-time classification on temporal data. The designed is implemented using lower hardware resources such as logic elements, multipliers and memory with better latency compared to existing hardware design of recurrent neural networks. Proposed model is validated for speech recognition and human activity classification.

Performed Bayesian Analysis for classification on MNIST and CIFAR-10 dataset. Used maximum likelihood estimation to determine the parameters of conditional density. Created a real-time demo to recognize user drawn handwritten digit.

Based on user voice commands, functioning of embedded system will be controlled. Through speech, user can control status of red, green, and blue LEDs on Tiva LaunchPad and can ask for temperature. In response system can greet the user, tell the temperature and reply whether it has received the command to control LED Lights.

Developed a learning mechanism for implementation of neural networks in FPGA or digital hardware. The proposed technique uses local learning and sign based approach to update weights. This add parallelism with reduced hardware while learning. Tested the mechanism using MNIST and CIFAR-10 database with RELU as activation function.

It was a bachelor thesis project. Developed a motherboard having FPGA of Spartan-3E family, with a 12-bit interface for Tiva LaunchPad (Evaluation Board by Texas Instrument). Image processing tasks such as edge detection and contrast enhancement were performed using hardware software co-design techniques.

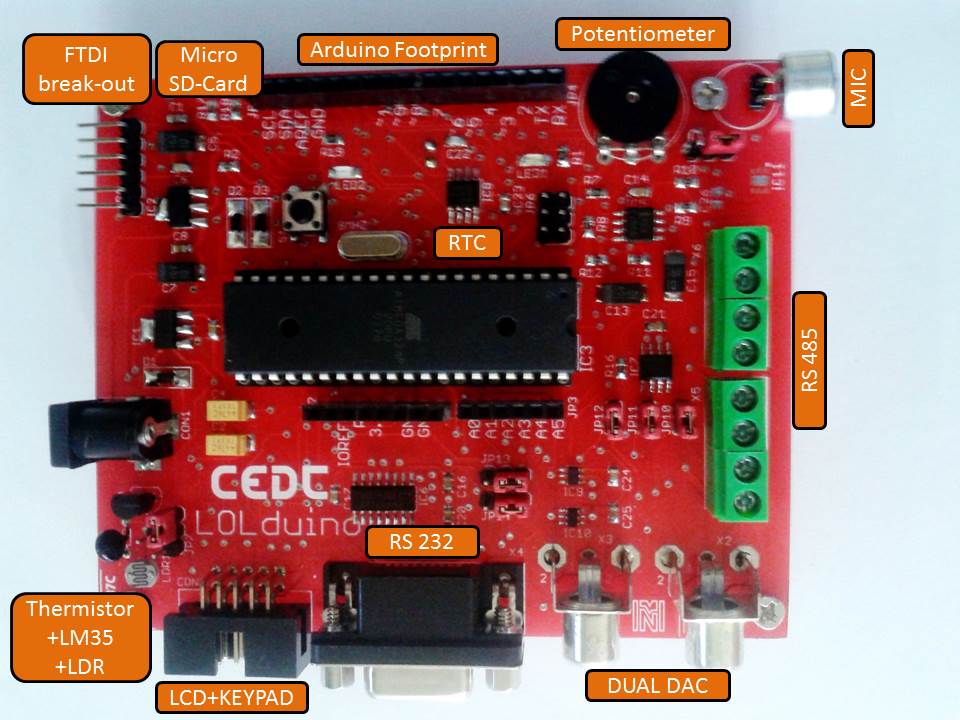

Designed a system using Atmega 324 having arduino generic footprint in addition to various features like temperature sensors, light sensors, electret microphone (MIC), potentiometer, DAC7571, real time clock (RTC), micro SD-Card, RS232/RS485, LCD and keypad. Here, arduino IDE was tweaked so that same can be able to program above Atmega324 based system. And, all current existing libraries for Arduino UNO are compatible with this system.

Designed a diagnostic unit using ARM Cortex-M3 based microcontroller which includes user electrocardiograph and pulse-oximeter with its user interface on television unit and TFT LCD.